Verilog Based Case Study Of D Flipflop Pdf Electrical Engineering

Verilog Based Case Study Of D Flipflop Pdf Electrical Engineering This document describes different ways to model a d flip flop in hardware description language including: gate level, behavioral, and structural modeling. it also discusses including a clear input to force the output to a known state and provides example code and simulated waveforms of d flip flops with and without clear inputs. This repository is a comprehensive collection of verilog hdl implementations showcasing 8 distinct variants of d flip flops (dffs). these fundamental building blocks of digital circuitry play a crucial role in storing and synchronizing digital signals.

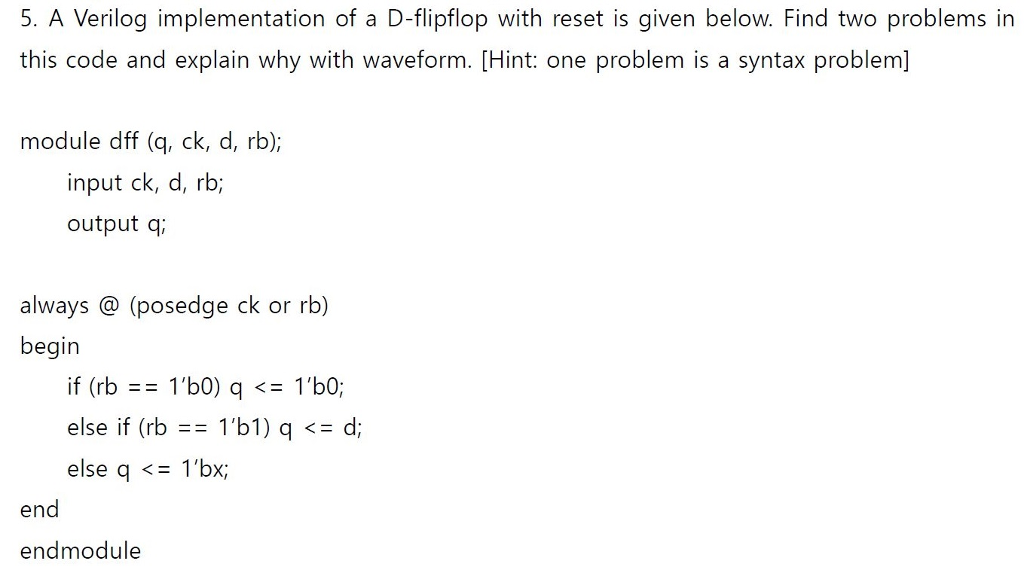

D Flipflop Pdf In this article, we will explore the design and implementation of the d flip flop using verilog through three key abstraction levels: gate level, dataflow, and behavioral modeling. Verilog code for d flip flop d flip flop is a fundamental component in digital logic circuits. verilog code for d flip flop is presented in this project. there are two types of d flip flops being implemented which are rising edge d flip flop and falling edge d flip flop. verilog code for rising edge d flip flop:. Write the verilog for a 2 input gate that is true when an odd number of inputs are true. the following two flip flops are subtly different, but both useful. the difference in code is shown in bold. what is the difference in their behavior? if (reset). In this book we use a modern design approach based on the verilog hardware description language and cad tools to illustrate many aspects of logic circuit design.

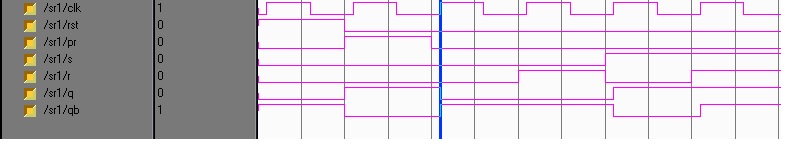

Hdl Code T D Sr Jk Flipflops Verilog Sourcecode Write the verilog for a 2 input gate that is true when an odd number of inputs are true. the following two flip flops are subtly different, but both useful. the difference in code is shown in bold. what is the difference in their behavior? if (reset). In this book we use a modern design approach based on the verilog hardware description language and cad tools to illustrate many aspects of logic circuit design. The article provides a comprehensive guide on designing a d flip flop using various modeling techniques, including gate level, dataflow, behavioral, and structural modeling. I'm pretty sure the d flip flop code is correct but when i try to test this my d and state values are just x for some reason. when i put in different x and y values in my testbench nothing happens, "state" and "d" just always says it has value "1'hx" in the simulation. This case study focuses on the modeling and simulation of a d flip flop using vivado software. it details the working principle, advantages, disadvantages, and applications of d flip flops, along with the procedure for creating a verilog code and testbench. Designed verilog code for d flip and verified its operation with simulation waveforms. learning outcome: after completion of this experiment, students are able to design d flip flop using verilog code.

Solved A Verilog Implementation Of A D Flipflop With Reset Chegg The article provides a comprehensive guide on designing a d flip flop using various modeling techniques, including gate level, dataflow, behavioral, and structural modeling. I'm pretty sure the d flip flop code is correct but when i try to test this my d and state values are just x for some reason. when i put in different x and y values in my testbench nothing happens, "state" and "d" just always says it has value "1'hx" in the simulation. This case study focuses on the modeling and simulation of a d flip flop using vivado software. it details the working principle, advantages, disadvantages, and applications of d flip flops, along with the procedure for creating a verilog code and testbench. Designed verilog code for d flip and verified its operation with simulation waveforms. learning outcome: after completion of this experiment, students are able to design d flip flop using verilog code.

Comments are closed.