Cache Computing Pdf Cache Computing Cpu Cache Answer: a n way set associative cache is like having n direct mapped caches in parallel. When virtual addresses are used, the system designer may choose to place the cache between the processor and the mmu or between the mmu and main memory. a logical cache (virtual cache) stores data using virtual addresses. the processor accesses the cache directly, without going through the mmu.

Cache Memory Pdf Cpu Cache Information Technology This document discusses computer memory and cache memory. it begins by explaining that cache memory is a small, fast memory located between the cpu and main memory that holds copies of frequently used instructions and data. Pdf | on oct 10, 2020, zeyad ayman and others published cache memory | find, read and cite all the research you need on researchgate. Cache: smaller, faster storage device that keeps copies of a subset of the data in a larger, slower device if the data we access is already in the cache, we win!. What to do then? any ideas? typically, a computer has a hierarchy of memory subsystems:.

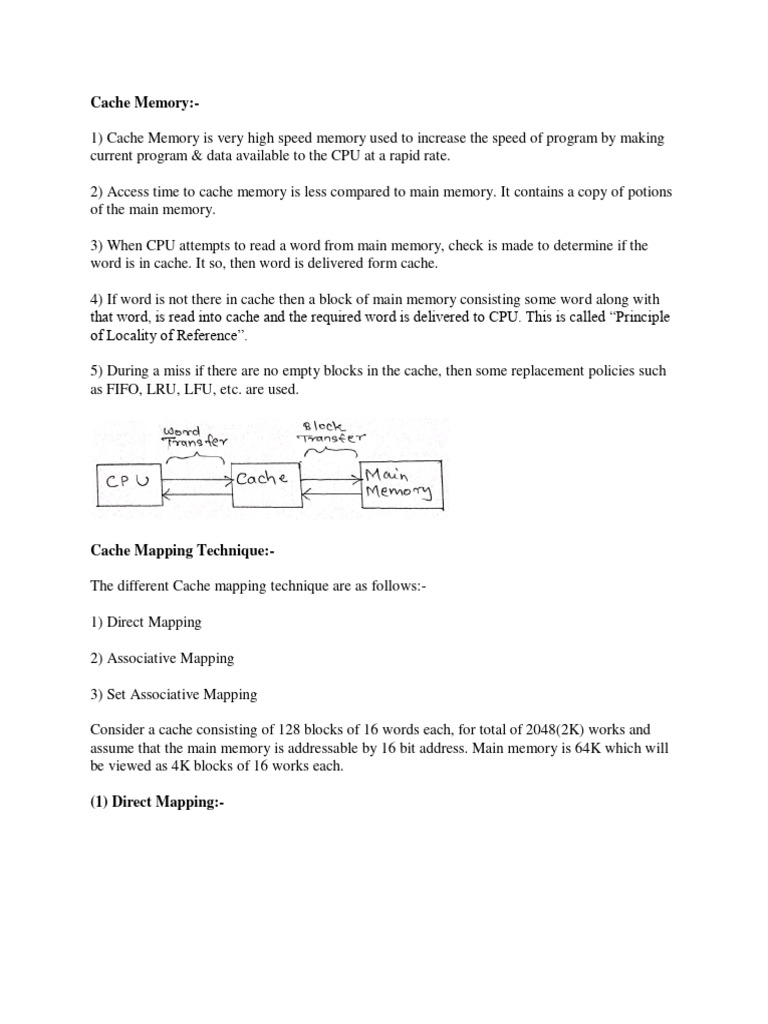

03 Chap4 Cache Memory Mapping Pdf Cpu Cache Computer Data Storage Cache: smaller, faster storage device that keeps copies of a subset of the data in a larger, slower device if the data we access is already in the cache, we win!. What to do then? any ideas? typically, a computer has a hierarchy of memory subsystems:. Caches are everywhere in computer architecture, almost everything is a cache! registers “a cache” on variables – software managed first level cache a cache on second level cache second level cache a cache on memory memory a cache on disk (virtual memory). • cache memory is a small amount of fast memory. ∗ placed between two levels of memory hierarchy. » to bridge the gap in access times – between processor and main memory (our focus) – between main memory and disk (disk cache) ∗ expected to behave like a large amount of fast memory. 2003. Cs 0019 21st february 2024 (lecture notes derived from material from phil gibbons, randy bryant, and dave o’hallaron) 1 ¢ cache memories are small, fast sram based memories managed automatically in hardware § hold frequently accessed blocks of main memory. This lecture is about how memory is organized in a computer system. in particular, we will consider the role play in improving the processing speed of a processor. in our single cycle instruction model, we assume that memory read operations are asynchronous, immediate and also single cycle.

Function Levels And Characteristics Of Cache Memory Know Computing Caches are everywhere in computer architecture, almost everything is a cache! registers “a cache” on variables – software managed first level cache a cache on second level cache second level cache a cache on memory memory a cache on disk (virtual memory). • cache memory is a small amount of fast memory. ∗ placed between two levels of memory hierarchy. » to bridge the gap in access times – between processor and main memory (our focus) – between main memory and disk (disk cache) ∗ expected to behave like a large amount of fast memory. 2003. Cs 0019 21st february 2024 (lecture notes derived from material from phil gibbons, randy bryant, and dave o’hallaron) 1 ¢ cache memories are small, fast sram based memories managed automatically in hardware § hold frequently accessed blocks of main memory. This lecture is about how memory is organized in a computer system. in particular, we will consider the role play in improving the processing speed of a processor. in our single cycle instruction model, we assume that memory read operations are asynchronous, immediate and also single cycle.